## Low voltage high bandwidth self-biased high swing cascode current mirror

Nikhil Raj<sup>a\*</sup>, Ashutosh Kumar Singh<sup>b</sup> & Anil Kumar Gupta<sup>c</sup>

<sup>a</sup>Department of Computer and Communication Engineering, Manipal University, Jaipur 302 006, India

<sup>b</sup>Department of Computer Application, National Institute of Technology, Kurukshetra 136 119 India

<sup>c</sup>Department of Electronics and Communication Engineering, National Institute of Technology, Kurukshetra 136 119 India

Received 1 April 2016; revised 31 October 2016; accepted 3 January 2017

A low voltage self-biased high swing cascode current mirror (SHCCM) with improved bandwidth has been proposed. The recently reported SHCCM architecture use the bulk-driven quasi-floating gate (BDQFG) MOS transistors to enhance the effective transconductance which improves the current mirror input resistance and bandwidth range over the same architecture realized using bulk-driven MOS transistors. To further improve the bandwidth the proposed BDQFG based SHCCM uses two resistances which makes the current mirror frequency response free from input capacitors and also reduces the parasitic capacitance effect which results in increased bandwidth with an advantage of having no degradation in other performance parameters of current mirror. The proposed current mirror operates well for input current range from 0 to 200  $\mu$ A with good linearity and shows the bandwidth of 298 MHz (i.e., 1.6 times over prior reported BDQFG based SHCCM). The observed input and output resistance is 306  $\Omega$  and 165 k $\Omega$ , respectively. Further, the THD analysis is carried to prove the robustness of proposed current mirror. The complete analysis is performed on UMC 0.18  $\mu$ m technology using HSpice.

Keywords: Bulk-driven MOS, Quasi-floating-gate MOS, Low-voltage, Current Mirror, Bandwidth

#### 1 Introduction

Prolonging the battery life time is the basic requirement of modern portable electronics and battery-powered implantable and wearable medical devices. In context to this, many efforts and techniques have been exerted for realizing circuits which can work at sub-volt supply<sup>1</sup>. The scaling of supply voltage strongly affects the performance of analog circuits and does not guarantee reliable performance since the threshold voltage does not scale down proportionally. The supply voltage must be at least equal to or greater than the threshold of MOS transistors used in circuit realization. So, using conventional technique for circuit design at sub-volt supply without sacrificing the desired performance has becomes a tedious task nowadays. Therefore, various techniques have been proposed in literature which reduces the threshold voltage effect or even remove it thereby facilitate the circuits to operate at low voltage (LV). Few techniques frequently adopted are categorized as subthreshold<sup>2</sup>, level shifter<sup>3</sup>, bulk driven (BD)<sup>4</sup>, floating gate (FG)<sup>5-7</sup>, quasi-floating gate (QFG)<sup>8-10</sup>. Among these the BD is found to be most suitable approach for realizing low voltage low power

Though using BD, FG and QFG techniques offer high functionality at low voltage low power capability these techniques have drawback of transconductance and low transition frequency. As a result, the circuits suffer reduced bandwidth and low gain structures. Besides, the FG and QFG based circuits also require large chip area. However, a most promising technique has been revealed in literature which congregates the characteristic of BD and FG/OFG MOS transistor. The technique is named as BDFG/BDQFG<sup>14</sup>, i.e., BD MOS transistor configured in FG/QFG mode. Using BDFG/BDQFG the structure results in enhanced transconductance over separate BD and FG/QFG MOSFET. Compared to QFG, the FG based circuits suffer few drawbacks such as charge trapping, poor transconductance, and poor bandwidth. In context to this BDQFG has gained considerable potential interest over BDFG. Few latest

circuits as it do not require any special arrangement for threshold voltage removal form input signal path. The bulk-input demand maximum supply not more than a BJT junction turn-on potential to prevent latchup and so the technique is found suitable for battery-operated portable devices. From literature survey it has been found that most of the recent publications are based on BD approach<sup>11-13</sup>.

<sup>\*</sup>Corresponding author (E-mail: nikhilpub@gmail.com)

research articles published has used the BDQFG technique in realisation differential difference current conveyor<sup>15</sup>, differential difference amplifier<sup>16</sup>, rectifier<sup>17</sup>, etc. Moreover, the recently published article has proved experimentally the advantage of using BDQFG technique for realizing low power circuits<sup>18,19</sup>. In this paper, a low voltage high bandwidth SHCCM based BDQFG MOSFET is presented.

Current mirror is the most important and fundamental block for analog circuits. Realizing current mirror with bulk as input requires very low supply voltage and best suits to low power devices. However, the BD based current mirrors have limited applications due to poor current matching, less operating range and smaller bandwidth due to low transconductance. The proposed current mirror increases the bandwidth of prior reported low voltage BDQFG SHCCM<sup>20</sup> without degrading any of other performance parameter and consuming the same level of power consumption.

# 2 Bulk Driven and Bulk Driven Quasi Floating Gate MOSFET

## 2.1 BD MOSFET

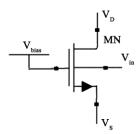

The conventional MOSFET is a four terminal device whose fourth terminal, the bulk is connected to negative/positive supply for N-channel/P-channel transistor, respectively, or to their source terminal. Using bulk as signal input removes the threshold voltage limitation from input path. The very first article used BD technique to design differential amplifier<sup>21</sup>. The schematic of N-channel BD MOSFET is shown in Fig. 1. The dc bias voltage  $V_{\text{bias}}$  at gate of transistor MN creates the channel whereas the input signal is applied at bulk which modulates the drain-to-source current even with very low amplitude of input signal.

The most significant drawback related to the bulk-driven is its small body transconductance  $(g_{mb})$  which is 3 to 5 times smaller than gate

Fig. 1 – N-channel BD MOS transistor

transconductance and poor transition frequency  $^{17}(f_T)$ . The  $g_{mb}$  relation with gate transconductance  $(g_{mb})$  is given as:

$$g_{mb} = \frac{y}{2\sqrt{2g_f - V_{SB}}}g_m = \eta g_m$$

... (1)

where  $\gamma$  is the body effect coefficient,  $\phi_f$  is the Fermi-potential,  $V_{SB}$  is the source-to-bulk potential. The normal range of  $\eta$  varies from 0.2 to 0.4. However, the bio-signals being small in amplitude and low frequency range suits the use of BD approach for signal processing which ranges in kHz.

#### 2.2 BDOFG MOSFET

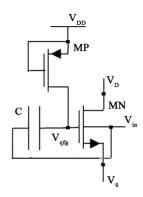

The schematic of N-channel BDQFG MOSFET MN is shown in Fig. 2. The input capacitor C along with P-channel MOS transistor MP forms QFG node for MN and its bulk acting as input tied to its respective gate forms the BDQFG structure. Under DC, the structure behaves as standard BD MOSFET whereas for AC analysis it combines characteristics of BD and QFG MOSFET. This results in effective transconductance higher than separate BD or OFG transconductance and also increased transition frequency  $(f_{\tau})$ . The effective transconductance  $(g_{meff})$  of BDQFG MOSFET is given as:

$$g_{meff} = kg_m + g_{mh} = (k + \eta)g_m$$

... (2)

where *k* is the effective capacitance ratio of input to the total capacitance seen at QFG of MN The comparative analysis on MOSFET parameters in saturation mode using BD and BDQFG technique is shown in Table 1.

Fig. 2 – N-channel BD-QFG MOS transistor

| Table 1 – Comparison of MOSFET parameters using BD and BDQFG technique |                  |                                                        |  |  |

|------------------------------------------------------------------------|------------------|--------------------------------------------------------|--|--|

| Parameter                                                              | BD               | BDQFG                                                  |  |  |

| Threshold                                                              | removed          | removed                                                |  |  |

| Transconductance                                                       | $(0.2-0.4)g_m$   | $(0.7-1)g_m$                                           |  |  |

| Output conductance                                                     | $\lambda I_{DS}$ | $\left(C_{gd,MP}/C_{T,qfg}\right)g_m + \lambda I_{DS}$ |  |  |

| Transition frequency                                                   | $(0.3-0.5)f_T$   | $(0.7-0.9)f_T$                                         |  |  |

## **3 Proposed Current Mirror**

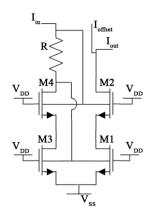

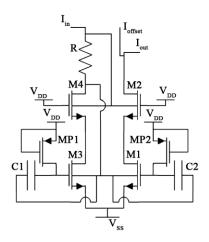

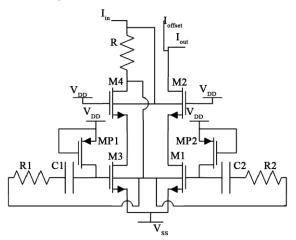

In deep submicron technology, the conventional two transistor based current mirror does not fulfill the required performance of ideal current mirror. The short channel MOS device often results high output conductance and hence poor current matching. In this context, the cascode current mirror<sup>22</sup> (CCM) was proposed which provide high output impedance and suits high performance applications like in design of second generation current conveyors, op-amps, LNA etc. Though the CCM offers high output impedance but its reduced output signal swing due to overdrive voltage required by output MOSFET puts limitation on its uses for circuits requiring rail-to-rail operation. However, this overdrive voltage requirement got reduced by placing a series resistance R at the drain contact of input MOS transistor and the architecture was named as self-biased high swing cascode current mirror<sup>23</sup> (SHCCM). The detailed analysis of this current mirror and its modification in terms of output resistance can be found in<sup>24</sup>. However, for low voltage operation this gate driven SHCCM was realized using only BD MOS transistors and this BD based SHCCM<sup>25</sup> which when compared with its gate driven counterpart showed an improvement not only in terms of low voltage operation but also resulted in improved performance parameters. However, the BD SHCCM has disadvantage of high input resistance, low output resistance and poor bandwidth. To enhance the performance the BD SHCCM when modified using BDQFG MOS transistor showed a significant improvement in terms of input resistance and bandwidth response<sup>20</sup>. The schematic of SHCCM based on BD and BDOFG reported in literature is shown in Figs 3 and 4, respectively.

In Fig. 3, the four BD N-channel MOS transistors  $(M_1-M_4)$  are used to realize the SHCCM. The use of offset current  $(I_{offset})$  at output node is for minimizing the mismatch between input and output current due to non-linear behavior of BD MOSFET at low supply.

Fig. 3 – Low Voltage BD based SHCCM<sup>25</sup>

Fig. 4 – Low voltage BDQFG based SHCCM<sup>20</sup>

Due to poor transconductance (i.e., body transconductance) of  $M_1$  and  $M_3$  MOSFETs, such current mirror results in not only high input resistance but also low bandwidth. The improvement to these parameters of current mirror was replacing these BD MOSFETs by BDQFG MOSFETs as shown in Fig. 4 where the  $M_3$  and  $M_1$  MOS transistor are replaced by BDQFG MOS transistor whereas  $M_2$  and  $M_4$  are kept in normal BD mode. However, the increased capacitances of BDQFG especially due to input capacitors, the enhancement in bandwidth is achieved till certain limit.

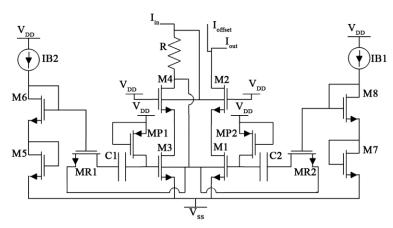

In proposed current mirror, the range of bandwidth is further increased by reducing the effect of input capacitances on the bandwidth response without degrading any other performance parameters. The architecture of proposed high bandwidth SHCCM based on BDQFG MOSFET is shown in Fig. 5. The modification is carried out by using resistance  $R_1$  and  $R_2$  in series to input capacitors  $C_1$  and  $C_2$ , respectively, of MOSFETs  $M_3$  and  $M_1$ , respectively.

Through analysis, it has been observed that using these resistors causes the circuit's frequency response gets independent of the effect of input capacitors and also to parasitic gate-to-source capacitances of  $M_1$  and  $M_3$  which results in bandwidth enhancement over prior architectures. Moreover, these resistors does not have impact on effective transconductance of  $M_1$  and  $M_3$  MOS transistor and so high bandwidth is achieved without degrading other parameters.

In Fig. 6, the resistors  $R_1$  and  $R_2$  realization is done using N-channel MOS transistors  $MR_1$  and  $MR_2$ , respectively. These MOS transistors  $MR_1$  and  $MR_2$  are made to operate in linear regime biased using N-channel MOS transistor  $(M_5, M_6)$  and  $(M_7, M_8)$ , respectively.

#### 3.1 Input resistance

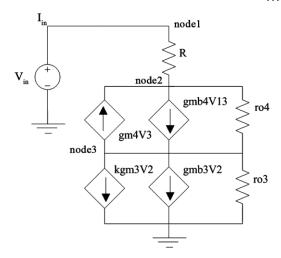

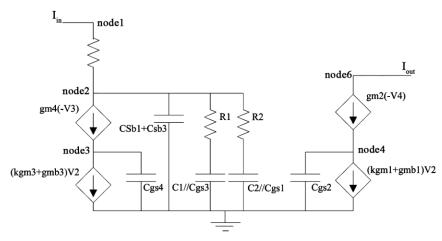

The small signal model for calculating the input resistance ( $R_{in,Proposed}$ ) of proposed current mirror is shown in Fig. 7 where:

Fig. 5 – Proposed low voltage BDQFG SHCCM with enhanced bandwidth

At node 2:

$$i_{in} = g_{mb4} (V_1 - V_3) - g_{m4} V_3 + \frac{V_2 - V_3}{r_{o4}}$$

... (3)

At node 3:

$$i_{in} = (kg_{m3} + g_{mb3})V_2 + \frac{V_3}{r_{o3}}$$

... (4)

$$V_2 = V_1 - i_{in}R$$

... (5)

Putting Eq. (5) in Eq. (4):

$$V_{3} = (1 + (kg_{m3} + g_{mb3})R)r_{o3}i_{in} - (kg_{m3} + g_{mb3})r_{o3}V_{1}$$

... (6)

From Eqs (3), (5) and (6):

$$R_{in} = \frac{V_1}{i_{in}} = \frac{\left(R\left(kg_{m3} + g_{mb3}\right)\left(g_{m4} + g_{mb4}\right)r_{o3}r_{o4} + \left(g_{m4} + g_{mb4}\right)r_{o3}r_{o4}\right)}{\left(kg_{m3} + g_{mb3}\right)\left(g_{m4} + g_{mb4}\right)r_{o3}r_{o4}}$$

$$(7)$$

Fig. 7 – Small signal model for calculating input resistance

Fig. 6 - Final proposed low voltage BDQFG SHCCM with enhanced bandwidth

Hence:

$$R_{in,Proposed} \approx R + \frac{1}{kg_{m,3} + g_{m,b,3}}$$

... (8)

Similar analysis when carried for BDQFG based SHCCM (Fig. 4) results in the input resistance as:

$$R_{in,BDQFG} \approx R + \frac{1}{kg_{m3} + g_{mb3}}$$

... (9)

And for the BD based SHCCM (Fig. 3), the input resistance is given by:

$$R_{in,BD} \approx R + \frac{1}{g_{mb3}} \qquad \dots (10)$$

From Eqs (8) and (9), no difference is observed in terms of input resistance. However, the advantage of using BDQFG in lowering of input resistance can be observed by comparing Eqs (8) and (9) with Eq. (10).

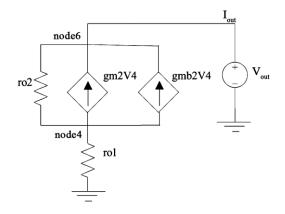

### 3.2 Output resistance

The small signal model for calculating the output resistance ( $R_{out,Proposed}$ ) of proposed current mirror is shown in Fig. 8 where:

At node 6:

$$i_{out} = -(g_{m2} + g_{mb2})V_5 + \frac{V_6 - V_4}{r_{o2}}$$

... (11)

At node 4:

$$V_4 = r_{o1} i_{out} \qquad \dots (12)$$

From Eqs (11) and (12):

$$i_{out} = -(g_{m2} + g_{mb2})r_{o1}i_{out} + \frac{V_6 - r_{o1}i_{out}}{r_{o2}} \qquad \dots (13)$$

Fig. 8 – Small signal model for calculating output resistance

$$R_{out} = \frac{V_6}{i_{out}} \approx r_{o1} + r_{o2} + (g_{m2} + g_{mb2}) r_{o1} r_{o2} \qquad \dots (14)$$

Since  $g_m r_o >> 1$

$$R_{out.Proposed} \approx (g_{m2} + g_{mb2}) r_{ol.afg} r_{o2} \qquad \dots (15)$$

Similar analysis when carried for BDQFG based SHCCM (Fig. 4) results in the output resistance as:

$$R_{out,BDQFG} \approx (g_{m2} + g_{mb2}) r_{o1,qfg} r_{o2} \qquad \dots (16)$$

And for the BD based SHCCM (Fig. 3), the output resistance is given by:

$$R_{out.BD} \approx (g_{m2} + g_{mb2}) r_{o1} r_{o2}$$

... (17)

From Eqs (15) and (16), no difference is observed in terms of output resistance whereas comparing with Eq. (17), due to increased output conductance of BDQFG MOS transistor  $M_1$  the degraded output resistance is achieved. The improvement to such low output resistance has been achived in the architectures<sup>26,27</sup> at the cost of increased power dissipation.

#### 3.3 Bandwidth

The small signal model for calculating the bandwidth ( $\omega_{0, \text{Proposed}}$ ) of proposed current mirror is shown in Fig. 9. The output conductance and the  $C_{gd}$  effects are neglected in comparison to  $C_{gs}$  of saturation mode transistors. Here,  $C_{sb}$  and  $g_{mb}$  are neglected in comparison to  $C_{gs}$  and  $g_{m}$  of  $M_2$  and  $M_4$ , respectively. In Fig. 9:

At node 3:

$$sC_{gs4}V_3 + (kg_{m3} + g_{mb3})V_2 + g_{m4}V_3 = 0$$

... (18)

$$V_3 = -\frac{\left(kg_{m3} + g_{mb3}\right)}{g_{m4} + sC_{gs4}}V_2 \qquad \dots (19)$$

At node 2

$$s\left(C_{sb1} + C_{sb3}\right)V_2 + \frac{V_2}{R_1 + \frac{1}{s\left(C_1 / / C_{gs3}\right)}} - g_{m4}V_3 + \frac{V_2}{R_2 + \frac{1}{s\left(C_2 / / C_{gs1}\right)}} + \frac{V_2 - V_1}{R} = 0$$

Assume  $C_1 = C_2$ ,  $C_{gs3} = C_{gs1}$ ,  $R_1 = R_2$

$$s(C_{sb1} + C_{sb3})V_2 + \frac{2s(C_1//C_{gs3})V_2}{1 + sR_1(C_1//C_{es3})} - g_{m4}V_3 - i_{in} = 0 \quad \dots (21)$$

Fig. 9 - Small signal model for calculating bandwidth

From Eqs (19), (20) and (21):

$$i_{in} = \frac{2C_{gs4}C_{sb1}}{\left(g_{m4} + sC_{gs4}\right)} \times \left(s^2 + \frac{g_{m4}}{C_{gs4}}s + \frac{g_{m4}\left(kg_{m3} + g_{mb3}\right)}{2C_{gs4}C_{sb1}}\right)V_2$$

... (22)

At node 6:

$$i_{out} = -g_{m2}V_4$$

... (23)

At node 4:

$$-g_{m2}V_4 = (kg_{m1} + g_{mb1})V_2 + sC_{gs2}V_4 \qquad \dots (24)$$

From Eqs (23) and (24):

$$i_{out} = \frac{g_{m2}}{g_{m2} + sC_{gr2}} (kg_{m1} + g_{mb1}) V_2 \qquad ... (25)$$

From Eqs (22) and (25):

$$A_{t} = \frac{i_{out}}{i_{in}} = \frac{g_{m2} (kg_{m1} + g_{mb1})(g_{m4} + sC_{gs4})}{2C_{gs4}C_{sb1}(g_{m2} + sC_{gs2})} \times \frac{1}{\left(s^{2} + \frac{g_{m4}}{C_{gs4}}s + \frac{g_{m4}(kg_{m3} + g_{mb3})}{2C_{gs4}C_{sb1}}\right)} \dots (26)$$

Let

$$g_{m2} = g_{m4}$$

,  $g_{mb2} = g_{mb4}$ ,  $g_{m3} = g_{m1}$ ,  $C_{gs2} = C_{gs4}$

$$A_{I} = \frac{i_{out}}{i_{in}} = \frac{g_{m2} (kg_{m1} + g_{mb1})/2C_{gs4}C_{sb1}}{\left(s^{2} + \frac{g_{m4}}{C_{ss4}}s + \frac{g_{m4} (kg_{m3} + g_{mb3})}{2C_{cs4}C_{sb1}}\right) \dots (27)$$

Hence:

$$\omega_{0,\text{Proposed}} = \sqrt{\frac{g_{m2}(kg_{m1} + g_{mb1})}{2C_{gs2}C_{sb1,3}}} \quad ... (28)$$

Similar analysis when carried for BDQFG based SHCCM (Fig. 4) results the bandwidth as:

$$\omega_{0,BDQFG} = \sqrt{\frac{g_{m2} \left( kg_{m1} + g_{mb1} \right)}{2C_{gs2} \left( C_{sb1,3} + \left( C_{1,2} / / C_{gs3,1} \right) \right)}} \quad \dots (29)$$

And for the BD based SHCCM (Fig. 3), the bandwidth is given by:

$$\omega_{0,BD} = \sqrt{\frac{g_{m2}g_{mb1}}{2C_{gs2}C_{sb1,3}}} \qquad ... (30)$$

Comparing Eqs (29) and (30), the increased transconductance of  $M_1$  results in high bandwidth for Fig. 4. However, the input capacitors and parasitic gate-to-source capacitances of  $M_3$  and  $M_1$  puts a limit on the bandwidth range. In this context, the proposed current mirror does not experience such effects and hence results in highest bandwidth as visible in Eq. (28).

## **4 Simulation Results**

The current mirrors shown in Figs 3, 4 and 6 are simulated on UMC 0.18  $\mu m$  mixed-mode twin-well technology at  $\pm\,0.2V$  supply with the help of HSpice simulator. The simulation results confirm the small signal analytical results. The MOS transistors width and length of referred current mirrors and proposed current mirror is listed in Table 2. The other assumed parameters for simulations are also listed in Table 2.

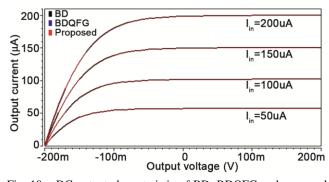

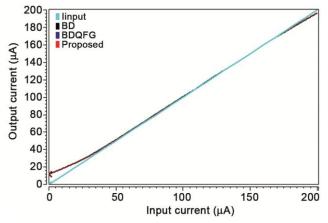

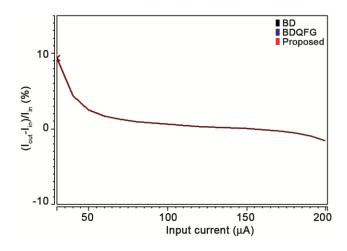

In Fig. 10, the output current is plotted in relation to output voltage for input current values till 200  $\mu A$  in steps of 50  $\mu A.$  As discussed, under DC conditions BDQFG behaves as BD MOS transistor so the overlapping for referred and proposed current mirror is observed. The overlapping of plots is also observed for current transfer characteristic shown in Fig. 11 for input current swept from 0 to 200  $\mu A$  and the

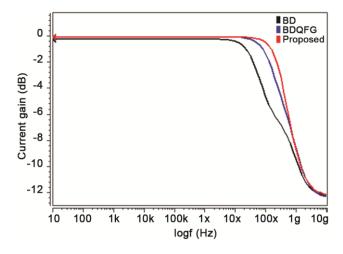

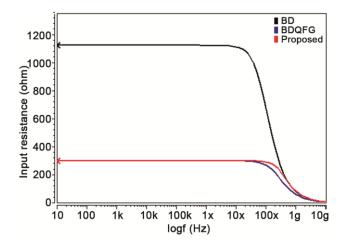

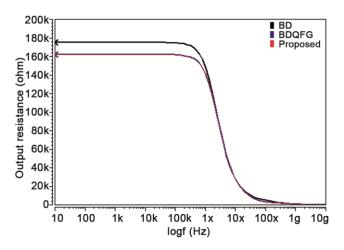

corresponding percentage error in current transfer is shown in Fig. 12. The frequency response is shown in Fig. 13. It is observed that the proposed current mirror shows the highest bandwidth of 306 MHz over BD and BDQFG which provide 80 MHz and 180 MHz respectively. Further, the input and output impedance is shown in Figs 14 and 15, respectively where a negligible variation can be observed between BDQFG and proposed but better than BD based SHCCM.

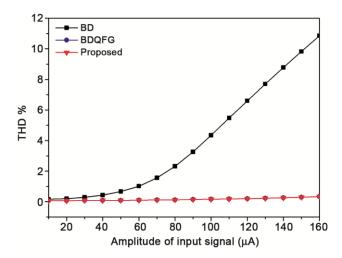

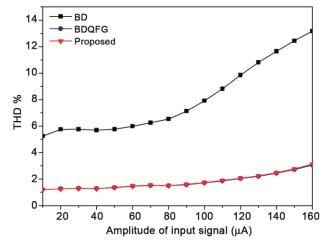

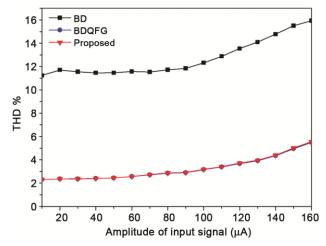

The non-linearity analysis of BD, BDQFG and proposed current mirror is shown with the help of total harmonic distortion (THD) calculation for

Table 2 - W and L of MOS transistors used in BD, BDQFG and proposed current mirror

| Transistors                                        | $W(\mu m)$ | $L (\mu m)$ | Transistors | $W(\mu m)$ | $L (\mu m)$ |  |

|----------------------------------------------------|------------|-------------|-------------|------------|-------------|--|

| $M_1$                                              | 207        | 0.54        | $M_7$       | 2.16       | 0.54        |  |

| $M_2$                                              | 207        | 0.54        | $M_8$       | 2.16       | 0.54        |  |

| $M_3$                                              | 207        | 0.54        | $MR_1$      | 10.08      | 0.54        |  |

| $M_4$                                              | 207        | 0.54        | $MR_2$      | 10.08      | 0.54        |  |

| $M_5$                                              | 2.16       | 0.54        | $MP_1$      | 0.36       | 0.36        |  |

| $M_6$                                              | 2.16       | 0.54        | $MP_2$      | 0.36       | 0.36        |  |

| $R=100 \Omega$ , $C1=C2=1$ pf, supply= $\pm 0.2$ V |            |             |             |            |             |  |

Fig. 10 - DC output characteristic of BD, BDQFG and proposed current mirror

Fig. 11 - Current transfer characteristics of BD, BDQFG and proposed current mirror

sinusoidal input current signal at frequency of 1 MHz, 10 MHz and 20 MHz at a quiescent current of 160  $\mu$ A. The THD percentages at above stated frequencies are shown in Figs 16–18. It is observed that with increase in input signal amplitude and frequency there is corresponding increase in THD percentage. The THD is found to be much better than simple BD SHCCM and remains around 5% even for 20MHz input signal. Also a very slight variation in THD is observed between BDQFG and proposed current mirror.

The complete HSpice simulation results are summarized in Table 3 which concludes that the proposed current mirror results in high bandwidth over prior arts at the same level of power consumption.

Fig. 12 – Percentage error in current transfer characteristics of BD, BDQFG and proposed current mirror

Fig. 13 - Frequency responses of BD, BDQFG and proposed current mirror

Fig. 14 – Input resistances of BD, BDQFG and proposed current mirror

Fig. 15 – Output resistance of BD, BDQFG and proposed current mirror

Fig. 16 – THD plot of BD, BDQFG and pProposed current mirror at 1MHz input sinusoidal signal

Fig. 17 – THD plot of BD, BDQFG and proposed current mirror at 10MHz input sinusoidal signal

Fig. 18 – THD plot of BD, BDQFG and proposed current mirror at 20MHz input sinusoidal signal

Table 3 – Comparative analysis on Current Mirror performance

| Reference<br>Parameters      | [25]      | [20]      | Proposed<br>BDQFG<br>SHCCM |

|------------------------------|-----------|-----------|----------------------------|

| Input current range (µA)     | 0-200     | 0-200     | 0-200                      |

| Input resistance $(\Omega)$  | 1.16 k    | 306       | 306                        |

| Output resistance $(\Omega)$ | 175 k     | 165 k     | 165 k                      |

| Bandwidth (MHz)              | 57        | 180       | 298                        |

| Supply (V)                   | $\pm$ 0.2 | $\pm$ 0.2 | ± 0.2                      |

| Technology (µm)              | UMC 0.18  | UMC 0.18  | UMC 0.18                   |

## **5 Conclusions**

In this paper, a high bandwidth BDQFG based SHCCM is presented. The achieved high bandwidth in without using any complex circuitry encourages its application for low power designs. The THD analysis carried proves the robustness of proposed current mirror. The complete analysis is carried out in

technology file of  $0.18~\mu m$  provided by UMC with the help of HSpice.

#### References

- Fayomi C J B, Sawan M & Roberts G W, Analog Integr Circuits Signal Process, 39 (2004) 21.

- Wang A, Clhoun B H & Chandracasan A P, Sub-threshold design for ultra low-power systems, (Springer, New York, USA), 2006.

- 3 Rajput S S & Jamuar S S, *IEE P-Circ Dev Syst*, 148 (2001) 273.

- 4 Blalock B J, Allen P E & Rincon-Mora G, *IEEE Trans Circuits Syst II*, 45 (1998) 769.

- 5 Hasler P & Lande T S, *IEEE Trans Circuits Syst II*, 48 (2001) 1.

- 6 Sharma S, Rajput S S, Pal K, Mangotra L K & Jamur S S, *Indian J Pure Appl Phys*, 44 (2006) 871.

- Manhas P S, Sharma S, Pal K, Mangotra L K & Jamwal K S, Indian J Pure Appl Phys, 46 (2008) 355.

- 8 Ramirez-Angulo J, Urquidi C, Gonzalez-Carvajal R, Torralba A & Lopez-Martin A, *IEEE Trans Circuits Syst II*, 50 (2003) 214.

- 9 Ramirez-Angulo J, Lopez-Martin A J, Gonzalez-Carvajal R & Munoz Chavero F, *IEEE J Solid State Circuits*, 39 (2004) 434

- 10 Raj N, Singh A K & Gupta A K, *Microelectron J*, 45 (2014) 1132.

- 11 Khateb F, Kumngern M, Vlassis S & Psychalinos C, Circuits Signal Process, 33 (2014) 159.

- 12 Vlassis S & Khateb F, *Electron Lett*, 50 (2014) 432.

- 13 Liang Z & Islam S K, IEEE Trans Circuit Syst I: Reg Papers, 60 (2013) 2084.

- Khateb F, AEU-Int J Electron Commun, 68 (2014) 64.

- 15 Khateb F, Jaikla W, Kumngern M & Prommee P, Microelectron J, 44 (2013) 1278.

- 16 Khateb F, Kumngern M, Vlassis S, Psychalinos C & Kulej T, Circuits Syst Comput, 24 (2015) 1550005-1.

- 17 Khateb F, Vlassis S, Kumngern M, Psychalinos C, Kulej T, Vrba R & Fujcik L, Circuits Signal Process, 34 (2015) 2077.

- 18 Khateb F, AEU-Int J Electron Commun, 69 (2015) 462.

- 19 Khateb F, Lahiri A, Psychalinos C, Kumngern M & Kulej T, AEU-Int J Electron Commun, 69 (2015) 1010.

- 20 Raj N, Singh A K & Gupta A K, Electron Lett, 50 (2014) 23.

- 21 Guzinski A, Bialko M & Matheau J C, Proc ECCD Paris, France, (1987) 315.

- 22 Allen P E & Holberg D R, CMOS analog circuit design, 2<sup>nd</sup> Edn. (Oxford University Press, New York), 2004.

- 23 Brooks T L & Rybicki M A, Self-biased cascode current mirror having high voltage swing and low power consumption, U.S. patent no. 5359296 (1994).

- 24 Gupta M, Aggarwal B & Gupta A K, Analog Integr Circuits Signal Process, 75 (2013) 67.

- 25 Aggarwal B, Gupta M & Gupta A K, Microelectron J, 44 (2013) 225.

- 26 Raj N, Singh A K & Gupta A K, *Microelectron J*, 52 (2016),

- 27 Raj N, Singh A K & Gupta A K, Circuit Syst Signal Process, 35 (2016) 2683.